泰克示波器MSO2系列在FPGA調試中的應用

FPGA (現場可編程門陣列)是由邏輯模塊和電氣程控互連組成的普通兩維陣列, 用來實現特定的硬件功能。 當前FPGA的設計速度、尺寸和復雜度明顯增長, 整個設計流程中的驗證和調試部分成為當前FPGA系統的關鍵部分。 由于獲得 FPGA 內部信號有限、FPGA 封裝和 PCB 電氣噪聲, 設計調試和檢驗變成設計周期中最困難的流程。 高速并行總線接口正迅速向高速串行接口方向發展, FPGA也不例外,每一條物理鏈路的速度從 600Mbps 到高達 10Gbps, 高速 IO 的測試和驗證更成為傳統專注于 FPGA 內部邏輯設計人員的巨大挑戰。 因此需要新的調試和測試工具,幫助調試設計,同時支持在 FPGA 上全速運行。

FPGA 調試挑戰

設計檢驗已經成為一個關鍵瓶頸

設計尺寸和復雜性提高

獲得內部信號受限

產品開發周期限制使調試時間縮短

調試時間可能會占設計周期的 50% 以上

簡單地查看外部針腳是不夠的

在 FPGA 中增加調試電路影響著設計

占用寶貴的芯片空間-要求額外的時間

可能會影響設計的定時性能

接入通常使用芯片上稀缺的針腳

可能很難測試板卡上的多個信號

傳統的 FPGA 調試方法主要包括以下兩種:

嵌入式邏輯分析儀

在設計中插入邏輯分析儀功能,擁有觸發和曲線存儲資源,使用 FPGA存儲器

缺點:

核心尺寸限制了其在大型 FPGA 中的使用

設計人員必須使用內存存儲曲線

存儲深度有限

只能在狀態模式下運行,速度有限

不能把FPGA曲線數據與其它系統曲線關聯起來

外部測試設備

使用全功能測試設備,把內部信號傳送到FPGA針腳上使用示波器、MSO 或邏輯分析儀觀察信號,使用FPGA的編程能力

缺點:

在每次試驗中,必須重新設計和編譯調試代碼

占用寶貴的 FPGA 門和針腳

查看復雜設計的能力在一定程度上受到針腳數量的限制

在MSO上必須手動更新信號名稱和通道指配

安泰測試介紹一種更好的解決方案:

FPGA 實時邏輯調試解決方案— FPGAView

優點:

可以實時調試 FPGA 適用于設計 Xilinx 和 Altera FPGA 的研發工程師

允許設計團隊查看 Xilinx 或 Altera FPGA 設計的內部運行情況

允許把這些信號與其它板卡信號關聯起來

提高工作效率,縮短調試時間

隨時切換內部測試點,不需要編譯 每個調試針腳調試多個內部信號

與其它調試方法相比,使用更簡便,插入性更低

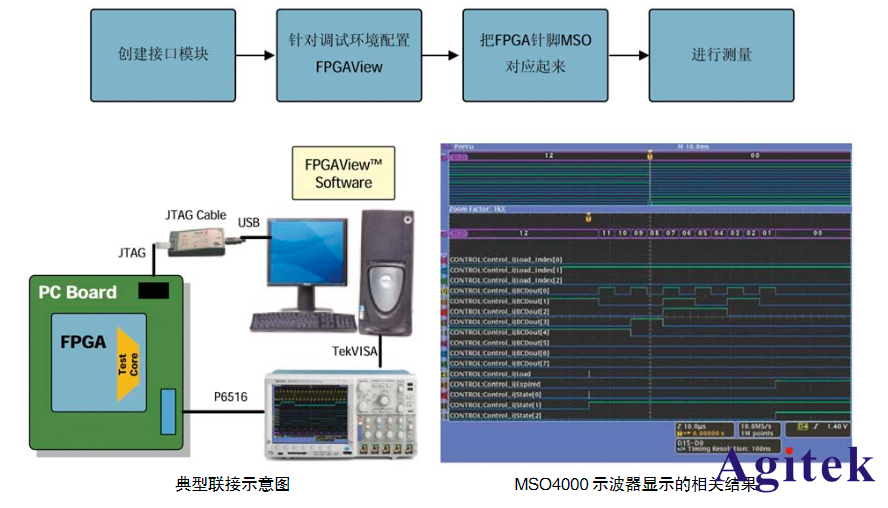

泰克示波器MSO2系測試步驟

泰克示波器MSO2系型號參數:

以上關于泰克示波器應用方案有安泰測試整理。關于更多示波器問題,歡迎咨詢安泰測試www.nfrol.com

關注官方微信

關注官方微信