DDR5技術(shù)演進與全鏈路測試解決方案深度解析

在數(shù)字化浪潮推動下,存儲器件已成為支撐現(xiàn)代電子系統(tǒng)的核心基礎(chǔ)設(shè)施。作為當(dāng)前主流的內(nèi)存技術(shù),DDR SDRAM(雙倍數(shù)據(jù)率同步動態(tài)隨機存取存儲器)歷經(jīng)五代技術(shù)迭代,其傳輸速率已突破6.4Gbps大關(guān),同時功耗較前代降低20%以上。這種指數(shù)級性能躍升背后,是信號完整性、時序精度和系統(tǒng)協(xié)同等測試維度的幾何級復(fù)雜度增長。本文將系統(tǒng)解析DDR5技術(shù)特性,并闡述其全鏈路測試解決方案。

一、DDR5技術(shù)架構(gòu)革新

DDR5標(biāo)準(zhǔn)在繼承前代技術(shù)精髓的基礎(chǔ)上,實現(xiàn)了三大維度突破:

性能維度:數(shù)據(jù)速率從DDR4的3200MT/s提升至6400MT/s,通過16n預(yù)取架構(gòu)將突發(fā)長度擴展至BL16,使內(nèi)存帶寬密度實現(xiàn)翻倍增長。

能效維度:工作電壓從1.2V降至1.1V,配合PMIC電源管理芯片實現(xiàn)動態(tài)電壓調(diào)節(jié),單位比特能耗降低達30%。

密度維度:單顆粒容量突破64Gb,通過32Bank Group架構(gòu)設(shè)計顯著提升并行訪問效率,特別適用于AI訓(xùn)練等高并發(fā)場景。

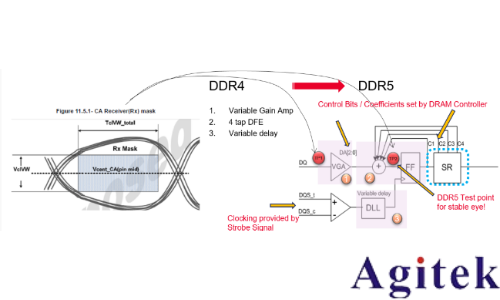

技術(shù)演進背后是底層架構(gòu)的顛覆性創(chuàng)新:DDR5首次引入SerDes技術(shù),采用DFE(決策反饋均衡)和CTLE(連續(xù)時間線性均衡)混合均衡方案,有效解決了高速信號傳輸中的ISI(碼間干擾)問題。同時,CA總線訓(xùn)練機制的引入,使時序參數(shù)從固定閾值轉(zhuǎn)向動態(tài)適配,這對測試系統(tǒng)的實時分析能力提出全新要求。

二、DDR5測試技術(shù)挑戰(zhàn)

面對6.4Gbps的信號速率,傳統(tǒng)測試方法遭遇三大瓶頸:

信號完整性分析:眼圖閉合程度加劇,要求測試設(shè)備具備≥50GHz帶寬和10bit垂直分辨率

抖動分解精度:需區(qū)分RJ(隨機抖動)、DJ(確定性抖動)等12類抖動成分,測量不確定度需控制在0.1ps以內(nèi)

協(xié)議解碼深度:需實時捕獲200層以上協(xié)議棧交互,支持PRBS31偽隨機序列的誤碼率測試

三、全鏈路測試解決方案

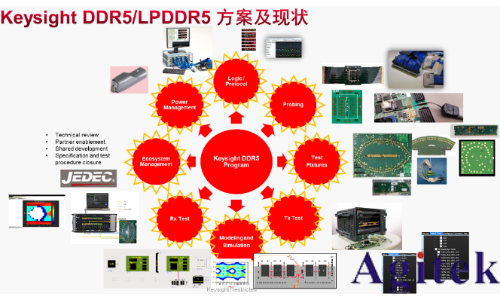

作為JEDEC標(biāo)準(zhǔn)制定核心成員,是德科技構(gòu)建了覆蓋物理層到協(xié)議層的完整測試體系:

1. 發(fā)射端測試方案

采用UXR系列110GHz實時示波器,配合D9050DDRC自動測試軟件,可實現(xiàn):

12類眼圖參數(shù)自動測量(Eye Height/Width/Mask等)

抖動成分分解(RJ/DJ/PJ/BUJ等)

預(yù)加重/去加重效果驗證

S-參數(shù)模型提取與信道仿真

2. 接收端測試方案

基于M8020A 32Gbps誤碼儀和UXR示波器,構(gòu)建閉環(huán)測試系統(tǒng):

支持DQS/DQ/CA總線靈敏度測試

DFE均衡器特性表征(Tap系數(shù)優(yōu)化)

應(yīng)力眼圖測試(Stressed Eye)

電壓/時序容限分析(Voltage/Timing Margin)

3. 協(xié)議層測試方案

U4164A邏輯分析儀搭載B4661A存儲器分析軟件,提供:

實時協(xié)議解碼(支持DDR5所有命令集)

200層以上協(xié)議棧追蹤

時序違規(guī)定位(Setup/Hold Time Violation)

功耗分布分析(Power Consumption Profiling)

4. 系統(tǒng)級測試方案

針對RDIMM/LRDIMM模塊,提供:

FS2600 Interposer夾具實現(xiàn)信號無損采集

W5643A BGA Interposer支持芯片級測試

電源完整性分析(PDN Impedance Measurement)

熱仿真與可靠性驗證

四、技術(shù)演進展望

隨著PCIe 6.0和CXL 3.0等高速協(xié)議的普及,DDR內(nèi)存測試正朝著"三超"方向發(fā)展:超高速率(12.8Gbps+)、超低抖動(<50fs RMS)、超寬頻帶(100GHz+)。是德科技最新推出的UXR0504A示波器,憑借110GHz帶寬和256GSa/s采樣率,為DDR6時代測試做好了技術(shù)儲備。

在AI算力爆炸式增長的背景下,DDR內(nèi)存測試已從單一參數(shù)驗證轉(zhuǎn)向系統(tǒng)級性能評估。通過構(gòu)建涵蓋設(shè)計仿真、信號采集、協(xié)議分析和系統(tǒng)驗證的全鏈路測試平臺,工程師能夠更高效地平衡性能、功耗和成本三大約束,加速下一代存儲產(chǎn)品的上市進程。

關(guān)注官方微信

關(guān)注官方微信