如何準(zhǔn)確測(cè)量電源噪聲

1.科技的發(fā)展對(duì)電源的要求越來(lái)越高

隨著科技的日益發(fā)展,電子產(chǎn)品上所用芯片的電源電壓也越來(lái)越小,從早期的5V逐步降低到了1.2V,某些芯片的核電壓甚至到了1V或更低。電壓越小,芯片對(duì)電壓波動(dòng)也變得越敏感。

通常用電源噪聲來(lái)表征電源電壓的波動(dòng),其要求通常是電源電壓的±5%到±1.5%,有的芯片要求甚至更低。如果芯片的電源噪聲沒(méi)有達(dá)到規(guī)范要求,輕則影響產(chǎn)品的性能,重則影響整機(jī)的可靠性。因此工程師需要準(zhǔn)確地測(cè)量電源噪聲。

▲圖1 日益發(fā)展的技術(shù)對(duì)電源要求越來(lái)越高

2.電源噪聲的特點(diǎn)

更小幅度,更高頻率

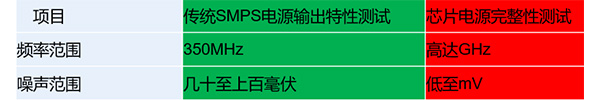

以往電源噪聲的幅度規(guī)范一般在幾十mV,但是隨著芯片電源電壓的降低,很多芯片的電源噪聲的規(guī)范已經(jīng)低至mV的量級(jí),某些對(duì)電源噪聲敏感的芯片要求甚至到了百u(mài)V的量級(jí)。

電源上的噪聲是數(shù)字系統(tǒng)中時(shí)鐘和數(shù)據(jù)抖動(dòng)的主要來(lái)源。處理器、內(nèi)存、模數(shù)轉(zhuǎn)換和 射頻等等芯片對(duì)直流電源的動(dòng)態(tài)負(fù)載隨著各自時(shí)鐘頻率而發(fā)生,還有可能在直流電源上耦合高速瞬態(tài)變化和噪聲,它們通常包含了GHz以上的頻率成分。

▲圖2 傳統(tǒng)電源和芯片電源對(duì)頻率范圍和噪聲幅度要求不同

因此與傳統(tǒng)的SMPS電源相比,芯片電源的噪聲具有頻率高/幅度小等特點(diǎn),這就使得工程師的測(cè)試工作充滿了挑戰(zhàn)---即如何準(zhǔn)確地測(cè)試分布在GHz帶寬內(nèi)mV級(jí)別的電源噪聲。

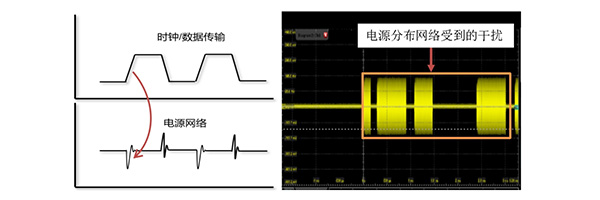

電源分布網(wǎng)絡(luò)(PDN)引入的噪聲干擾

為了保證電路上各個(gè)芯片的供電,電源分布網(wǎng)絡(luò)(PDN)遍布整個(gè)PCB。如果電源分布網(wǎng)絡(luò)靠近時(shí)鐘或者數(shù)據(jù)的PCB走線,那么時(shí)鐘/數(shù)據(jù)的變化會(huì)耦合到電源分布網(wǎng)絡(luò)上,也會(huì)成為電源噪聲的來(lái)源。

在這種情況下,工程師還需要定位電源噪聲的來(lái)源,以便后續(xù)調(diào)整電子產(chǎn)品的PCB布局和布線,減少PDN網(wǎng)絡(luò)受到的干擾。

▲圖3 時(shí)鐘/數(shù)據(jù)傳輸線耦合到電源分布網(wǎng)絡(luò)的干擾

3.影響電源噪聲測(cè)試準(zhǔn)確性的因素

示波器是電源噪聲測(cè)試的重要儀器。為了能夠準(zhǔn)確地測(cè)量GHz帶寬內(nèi)mV級(jí)別的電源噪聲,并定位干擾電源分布網(wǎng)絡(luò)的噪聲來(lái)源,需要考慮如下因素:示波器的底噪,探頭的衰減比,測(cè)試系統(tǒng)的偏置補(bǔ)償能力,探頭的探接方式,以及示波器的FFT能力等等。

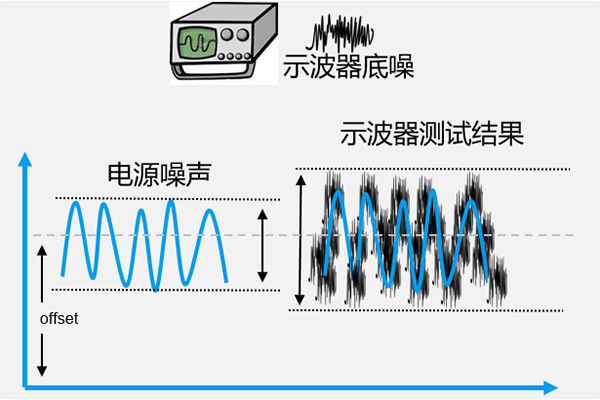

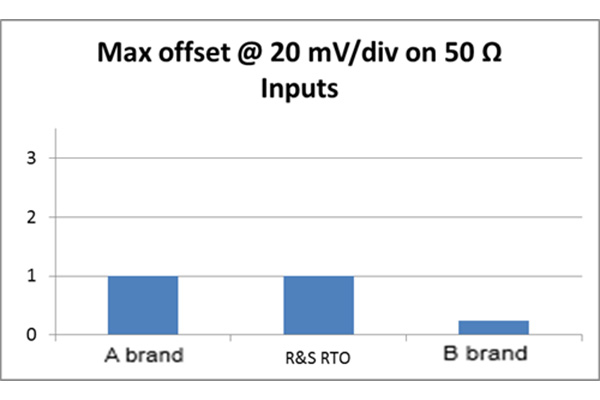

示波器的底噪

示波器本身是有底噪的。當(dāng)示波器測(cè)試電源噪聲時(shí),其自身的底噪會(huì)疊加在被測(cè)的電源噪聲上。如果示波器本身的底噪很大,那么會(huì)嚴(yán)重影響電源噪聲的測(cè)試準(zhǔn)確度。

▲圖4 示波器底噪對(duì)電源噪聲測(cè)試結(jié)果的影響

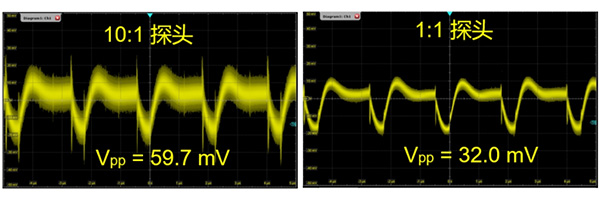

探頭的衰減比

業(yè)界最常用的500MHz帶寬的無(wú)源探頭的衰減比為10:1,其會(huì)將示波器的底噪放大十倍,導(dǎo)致電源噪聲測(cè)試的不確定性。

如果采用傳統(tǒng)的衰減比為1:1的無(wú)源探頭,可以避免放大示波器的底噪。但是這種探頭的帶寬通常只有38MHz,無(wú)法測(cè)到更高頻率的電源噪聲。同樣會(huì)導(dǎo)致電源噪聲測(cè)試的不確定性。

如左下圖,10:1的無(wú)源探頭測(cè)試電源噪聲明顯偏大;右下圖的1:1無(wú)源探頭測(cè)得電源噪聲正常,但是高頻的毛刺無(wú)法顯示。

▲圖5 探頭的衰減比對(duì)電源噪聲測(cè)試的影響

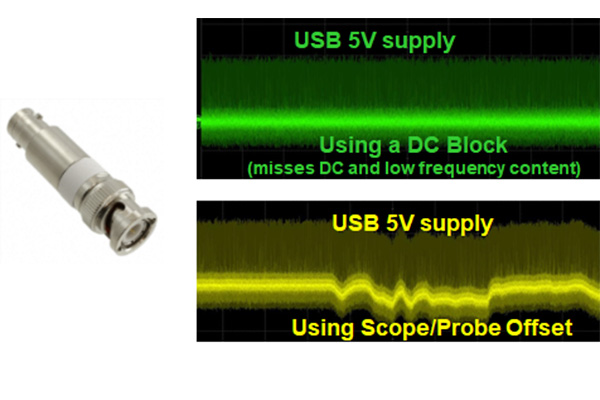

示波器的偏置補(bǔ)償能力

電源噪聲是疊加在電源電壓上的,為此測(cè)試時(shí)需要將示波器的偏置電壓設(shè)到與直流電壓相等的水平,再測(cè)量電源的噪聲。例如某芯片的供電電壓是3.3V,首先將示波器的偏置電壓調(diào)到3.3V,然后再測(cè)試3.3V直流電源上的mV級(jí)別的噪聲波動(dòng)。

但是示波器的垂直刻度的擋位受限于偏置電壓,在該偏置電壓下垂直刻度只能到20mV/div。用20mV/div的垂直刻度測(cè)試mV級(jí)別的電源噪聲,顯然會(huì)帶來(lái)很大的誤差。

為了解決類(lèi)似問(wèn)題,通常會(huì)使用隔直電容(或DC-Block)去除電源的直流電壓,但如此操作會(huì)導(dǎo)致直流電源壓縮和丟失電源的低頻特征。此外如果電容的容值選取不當(dāng),還會(huì)影響高頻噪聲的測(cè)量準(zhǔn)確性。

▲圖6 示波器的偏置補(bǔ)償能力受限

▲圖7 隔直電容影響低頻特征

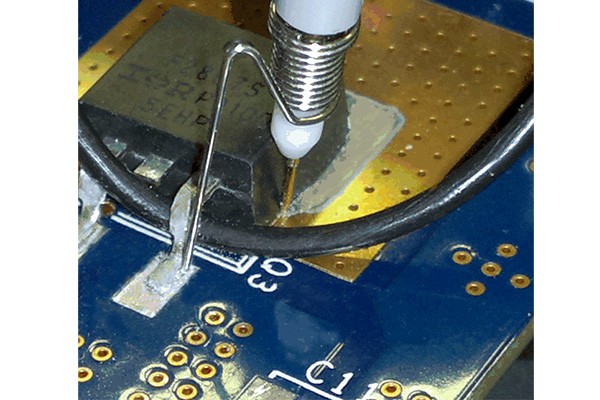

探頭的探接方式

電路形態(tài)各異,需要有更靈活的方法來(lái)進(jìn)行信號(hào)的探接。探接的穩(wěn)定性和寄生參數(shù)對(duì)被測(cè)電源電路的影響不可忽視,所以需要盡量貼近芯片的管腳,并使用短地線。

▲圖8 探頭貼近芯片管腳,使用短地線

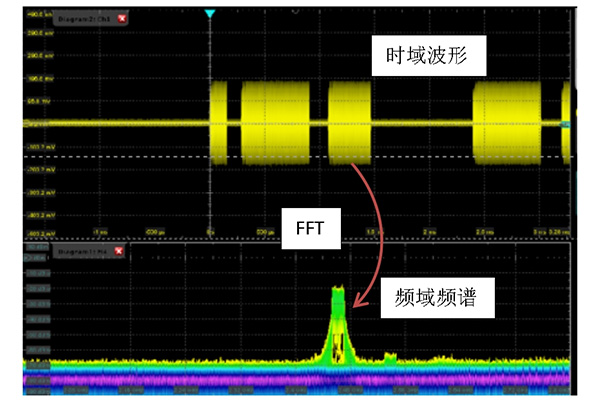

示波器的FFT能力

由于電源分布網(wǎng)絡(luò)PDN會(huì)受到干擾噪聲的來(lái)源,因此需要示波器具有強(qiáng)大的FFT分析能力,以便分析的干擾噪聲的頻率,進(jìn)而排查噪聲的源頭。

▲圖9 FFT分析電源噪聲的頻譜

4.羅德與施瓦茨(R85)電源噪聲測(cè)試方案

為了準(zhǔn)確地測(cè)量電源噪聲,R&S提供了示波器主機(jī)和專(zhuān)門(mén)的Power Rail電源軌探頭。

測(cè)試儀器

R&S推出的MXO5和MXO4系列示波器,帶寬最大2GHz,采用了12bit位數(shù)的ADC(HD模式下,分辨最低可達(dá)18bit),使得示波器的底噪在百u(mài)V級(jí)別,垂直刻度擋位最小可達(dá)0.5mV/div(硬件實(shí)現(xiàn),非放大),使得準(zhǔn)確測(cè)量GHz帶寬內(nèi)mV級(jí)別的電源噪聲成為可能。該系列示波器還具有強(qiáng)大的頻譜分析功能,幫助工程師快速排查干擾噪聲的來(lái)源。

▲圖10 MXO5示波器(上)和MXO4示波器(下)

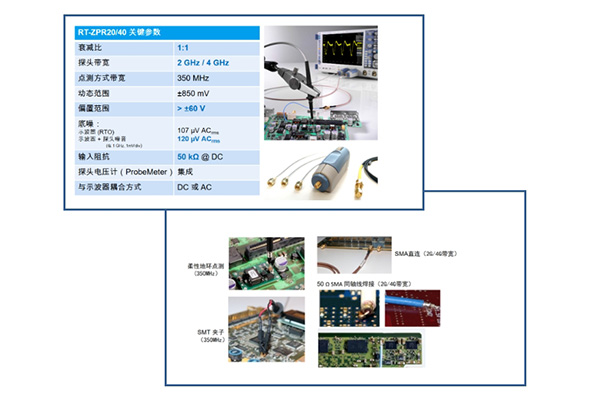

Power Rail電源軌探頭RT-ZPR20(2GHz) / RT-ZPR40(4GHz)具有優(yōu)異的性能,專(zhuān)門(mén)為電源測(cè)試量身打造。

其主要特性有:

1、在2GHz/4GHz帶寬內(nèi)具備1:1的衰減比,保證能夠測(cè)試到GHz帶寬mV級(jí)別的電源噪聲;

2、探頭具有50Kohm的高直流輸入阻抗,相對(duì)毫ohm級(jí)別阻抗的電源平面,可以最大程度地降低對(duì)待測(cè)電源的影響;

3、探頭內(nèi)置±60V的偏置能力,提升測(cè)試系統(tǒng)的偏置補(bǔ)償能力。測(cè)試電源噪聲時(shí),使用探頭內(nèi)部的偏置與待測(cè)電源保持一致,示波器的垂直刻度的擋位可以調(diào)至最小的0.5mV/div;

4、探頭內(nèi)部集成了16位數(shù)字電壓計(jì),實(shí)現(xiàn)同步讀取被測(cè)電源的直流電壓數(shù)值,并且可以一鍵精準(zhǔn)設(shè)置測(cè)試系統(tǒng)的偏置電壓;

5、專(zhuān)用的同軸探測(cè)線纜可焊接到電源濾波電容的兩端,點(diǎn)測(cè)附件則便于PCB上不同位置的輕松探測(cè)。

▲圖11 RT-ZPR系列探頭性能指標(biāo)及各種連接方式

測(cè)試實(shí)例

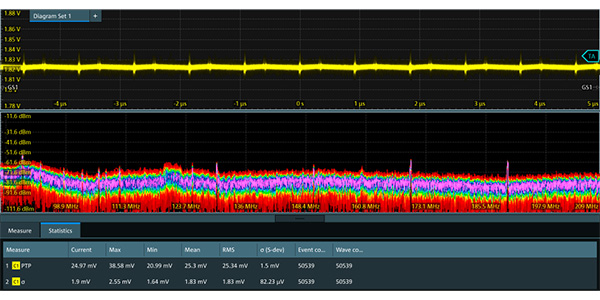

下面介紹利用MXO5示波器和Power Rail電源軌探頭RT-ZPR20測(cè)試電源噪聲,并排查噪聲來(lái)源的實(shí)例。

▲圖12 一次探接即可獲得電源噪聲以及干擾源

將RT-ZPR20探頭連接到測(cè)試點(diǎn)后,按照如下操作進(jìn)行測(cè)試:

1.RT-ZPR20內(nèi)置電壓計(jì)實(shí)現(xiàn)高精度DC電壓測(cè)試,測(cè)得電源電壓為1.82V;

2.RT-ZPR20的偏置電壓設(shè)到1.82V附近,并將示波器垂直刻度設(shè)到10mV/div;

3.示波器測(cè)得電源噪聲波形,從時(shí)域波形上發(fā)現(xiàn)有明顯的干擾噪聲;

4.對(duì)電源噪聲幅值進(jìn)行測(cè)試與統(tǒng)計(jì);

5.得到電源噪聲頻譜,根據(jù)噪聲頻率分析噪聲來(lái)源。

關(guān)注官方微信

關(guān)注官方微信