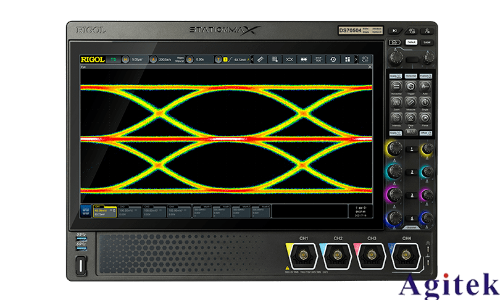

普源DS70000的5GHz實時采樣技術架構剖析

普源(Rigol)DS70000系列示波器作為高端數字示波器中的佼佼者,其5GHz實時采樣技術是其核心競爭力之一。本文將從總體架構、關鍵技術和實現優勢三個方面,對DS70000系列的5GHz實時采樣技術進行深入剖析,揭示其在高速采集和高精度信號捕獲中的技術秘密。

一、總體技術架構概述

普源DS70000示波器采用模塊化設計,關鍵采樣鏈路主要包括:

多通道高速采樣系統

支持單通道5GHz帶寬,典型采樣率可達40GSa/s,滿足高速數字信號和射頻信號的采集需求。

高性能模數轉換器(ADC)

采用先進的高速、低噪聲ADC芯片,保持寬帶寬下高動態范圍和高分辨率。

高速信號預處理單元

包含低噪聲前端放大和帶寬限幅電路,保證輸入信號在ADC前得到良好匹配和濾波。

FPGA實時數據處理平臺

負責高速數據流管理、觸發判決、序列重組和顯示處理,實現真正的實時采樣和波形顯示。

二、關鍵技術細節剖析

1. 多階采樣技術

DS70000通過創新的多階采樣電路設計,優化信號路徑,減少信號失真,提升帶寬。多級放大器和帶通濾波器鏈路確保信號幅度和相位準確傳遞,避免采樣時的帶寬損失。

2. 先進ADC架構

選擇高采樣率ADC芯片,采用分時復用或時間交錯(time-interleaving)架構,多個ADC芯片協同工作提升總采樣速率,同時內部采用校準算法消除時間和增益不匹配帶來的采樣誤差。

3. 低抖動時鐘系統

5GHz下采樣對時鐘抖動極為敏感。DS70000集成低抖動、高穩定性的時鐘源和相位鎖定環(PLL),保證時鐘準確同步,極大降低抖動誤差,保證采樣精度。

4. 實時FPGA處理平臺

利用高速FPGA對采樣數據進行流水線處理,實現波形重建、去噪和觸發判斷,確保5GHz信號可以在實時模式下無丟失地捕獲和顯示。FPGA還支持多通道數據的實時合成和協議解碼。

三、實時采樣技術優勢

高速大帶寬信號完整捕獲

5GHz帶寬結合超高采樣率,確保高速數字總線和射頻信號的細節完整顯示,適合高速通信和高頻電子領域分析。

低噪聲高靈敏度

采用低噪聲放大與濾波設計,提升信噪比,捕獲微弱信號細節,增強測量可靠性。

高級時序同步

多通道時序同步誤差控制在皮秒級,適合多路高速信號的協同分析。

強大觸發能力

支持復雜觸發邏輯、實時采樣觸發與數學運算觸發,滿足復雜信號特征捕獲需求。

四、應用實例簡析

在高速串行總線調試(如PCIe Gen4/5)、射頻信號分析和高速模數轉換器測試中,DS70000的5GHz實時采樣架構表現卓越,能夠捕捉極短脈沖、精確測量抖動和噪聲,為信號完整性評估提供強力工具。

普源DS70000系列示波器的5GHz實時采樣技術通過創新的多階采樣電路、先進的高速ADC、低抖動時鐘系統及高性能FPGA處理,實現了高速、大帶寬信號的高精度、實時捕獲。其技術架構兼顧了采樣精度、處理速度和穩定性,是現代高頻高速電子測量領域的關鍵利器,為用戶提供了高度可靠的信號分析解決方案。

關注官方微信

關注官方微信